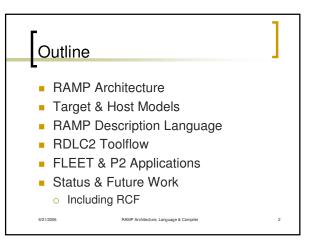

# RAMP: Architecture, Language & Compiler http://ramp.eecs.berkeley.edu Greg Gibeling, Andrew Schultz & Krste Asanovic gdgib@berkeley.edu 6/21/2006

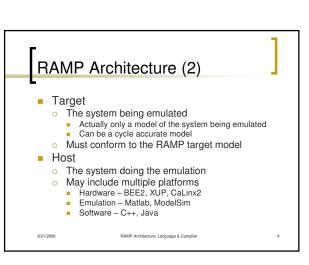

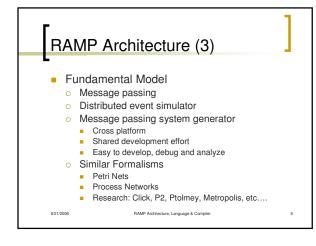

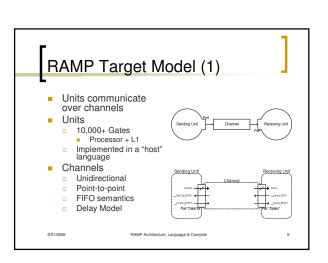

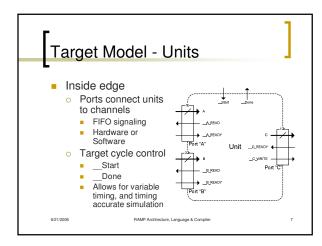

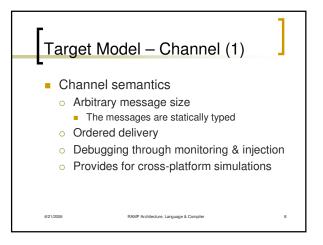

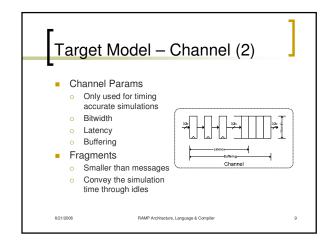

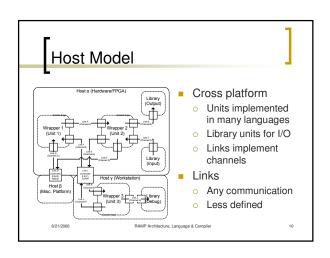

### RAMP Architecture (1) A framework for system emulation Massively parallel (digital hardware) systems Orders magnitude performance enhancement Leverage existing designs Allow community development Share designs, validate experiments, etc... Flexible, cross platform designs Requires proper structure Support for automatic debugging Automatic glue logic/code generation Based on the "target model"

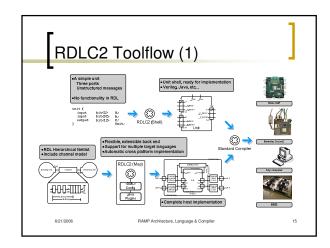

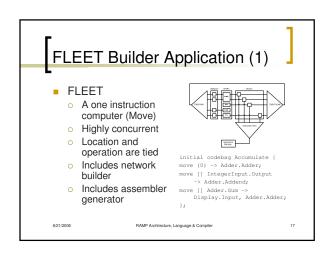

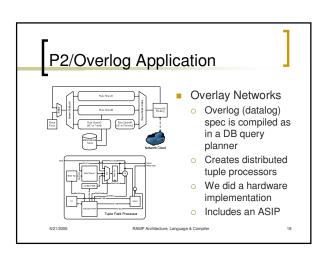

## State of the Project (1) ■ Working hardware O Compiled RDL to Verilog FLEET Processor & Assembler Builder Implementation of P2 overlay network platform in hardware Tested on CaLinx2, XUP, Digilent S3 and ModelSim SE RDL Changes Added RDL Features Added RDL Features Added compile time unit parameters Implemented hardware generators Similar in concept to Xilinx CoreGen Trivial lexical changes Required to support higher order ports and parameters

#### Future Work (1) RDL & RDLC3 Features Parameter Inference Problems The algorithm isn't always (easily) predictable Flesh out back end features More languages, platforms, links Debugging automation Automated test code generation for links and units Documentation Architecture, Language & Compiler Technical Report Complete compiler Javadocs Example and Tutorials

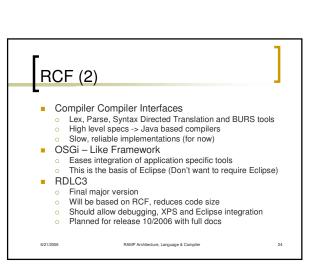

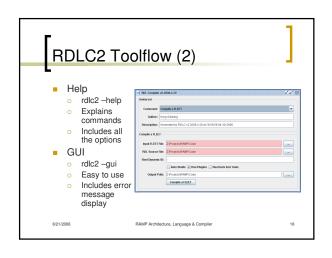

#### RCF – RAMP Compiler Framework Motivation Current parser & lexers are limited/buggy Application Specific Compilers FLEET & P2 required compilers Need to integrate these with RDLC RDLC2 still includes a lot of copy & paste 150,000 lines of java code! Bad for maintenance and upgrades Hard (almost impossible) to fix parameter inference without changing the core algorithms